Video/HDMI/LVDS/24-Bit-Parallel

Wir haben ein Video-Interface von HDMI auf Single-Plane-LVDS- und 24-Bit-Parallel-Ausgang

entwickelt.

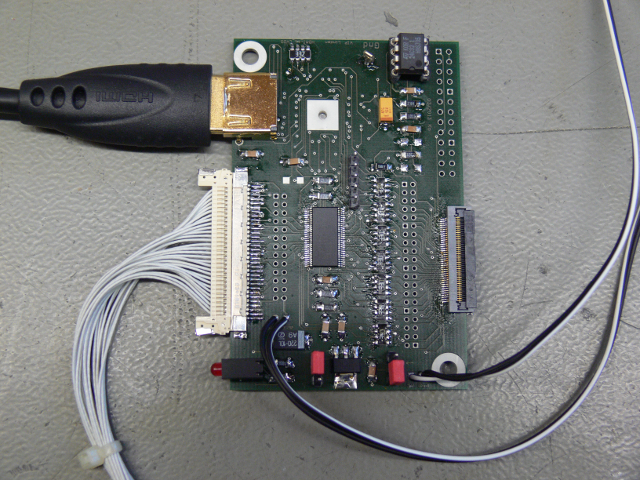

Entwicklungsmuster HDMI-to-LVDS Interface (links: HDMI und LVDS, rechts 24-Bit-Parallel, oben EEPROM, HDMI-Receiver ist auf Rückseite, CPLD/FPGA fehlt noch), Größe entspricht Raspberry Pi Format

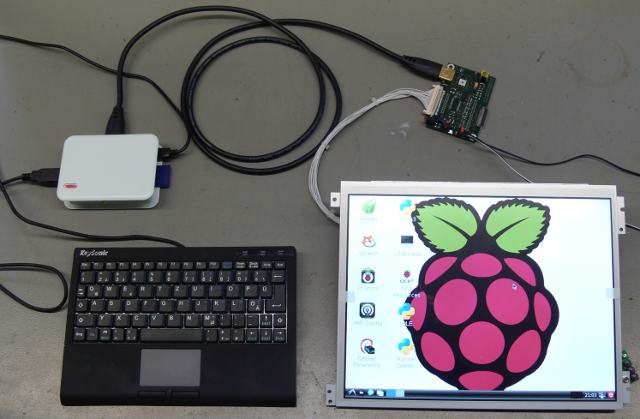

Entwicklungsmuster HDMI-to-LVDS-Interface mit Raspberry Pi und Kyocera-LVDS-Display TCG121SVLQ*PNN-AN*13 (800 x 600,75Hz) |

HDMI-to-LVDS-InterfacePreis auf Anfrage |

VIP HDMI-to-LVDS-Interface auch für

Raspberry Pi Der kostengünstige checkkartengrosse Computer Raspberry Pi hat als Standard-Video-Schnittstelle einen HDMI-Ausgang neben einem DSI- und Composite-(FBAS)-Ausgang. An den HDMI-Aushang kann man problemlos aktuelle Monitore mit einer Auflösung bis zu 1980 x 1080 anschliessen. Schwieriger gestaltet sich der Anschluß von nackten LC-Displays. Diese haben verschiedene Video-Interfaces: - Single-Plane LVDS mit 4x Differential-Daten-Lanes + 1x Differential-Clock-Lane für 24-Bit-Anschluß - Single-Plane LVDS mit 3x Differential-Daten-Lanes + 1x Differential-Clock-Lane für 18-Bit-Anschluß - Double-Plane LVDS mit 8x Differential-Daten-Lanes + 1x Differential-Clock-Lane für 48-Bit-Anschluß - Double-Plane LVDS mit 6x Differential-Daten-Lanes + 1x Differential-Clock-Lane für 36-Bit-Anschluß - Paralleler Datenanschluß mit 18-Bit oder 24-Bit Für den 18-Bit-LVDS-Anschluß müssen die Datenbit's auf anderen LVDS-Lanes umgelenkt werden. Es gibt zwar einen VESA-Standard für den physikalischen LVDS-Anschluß (Steckverbindung) von LC-Displays, aber kaum ein Hersteller hält sich daran. Daraus entsteht dann eine Unzahl von oft teueren Video-Verbindungsleitungen. Noch schwieriger wird es bei der Betrachtung der Synchron-Signale HSync und VSync. Es kann über die HDMI-Verbindung ein EEPROM (auf Seiten des LC-Displays) mit sogenannten EDID-Daten (128 Byte) abgefragt werden. Darin sollen alle Kenndaten des LC-Displays wie Auflösung, Bildwiederholrate und Lage der Sync-Signale enthalten sein. Sowohl der PC (mit Windows oder Linux) als auch der Raspberry Pi (Debian usw.) unterstützen das Auslesen dieses EEPROM's beim Booten, stellen daraus auch die beste Auflösung und Bildwiederholfrequenz her, ignorieren aber die Lage der Synchron-Signale. Viele LC-Displays bleiben deshalb dunkel. Ursache ist das der Vergleich der LC-Display EDID-Daten mit den VESA-Standardlisten für Monitore (DMT) und TV-Geräte (CVT) stattfindet und das Gewicht auf Auslösung und Bildwiederholfrequenz liegt. Bis 640 x 480 Auflösung sind die Sync-Signale dieser VESA-Listen meistens negativ, ab 800 x 600 Auflösung überwiegend positiv. Zum Schluß kommt noch die hohe Datenrate der HDMI-Schnittstelle mit bis zu 3.2GBit/s ins Spiel. Ein HDMI-to-LVDS-Interface besteht deshalb aus 4 wichtigen Komponenten: 1. HDMI-Receiver mit Parallelausgang 24 Bit / 48 Bit 2. CPLD- oder FPGA zum Umverdrahten der parallelen Datenleitung nach HDMI-Receiver wegen 18- und 24-Bit LVDS-LC-Displays und Möglichkeit die Sync-Signale zu invertieren. 3. LVDS-Transmitter für Wandlung 24-Bit / 48 Bit Parallel nach LVDS 4. 1kBit-EEPROM mit EDID-Daten für das LC-Display. Man kann auch die Punkte 1 bis 5 in ein FPGA programmieren (LatticeECP3 mit integrierten SERDES channel @ 3.2GBit für die HDMI-Verbindung) An einer serienmäßigen Leiterplatte arbeiten wir. |